# **DATA SHEET**

# gm5060/gm5060-H

Sections in this document and all other related documentation that mention HDCP refer only to the gm5060-H (HDCP-enabled) chip. All other sections apply to both the gm5060-H chip and the gm5060 (non-HDCP) chip.

Publication number: C5060-DAT-01G

Publication date: February 2002

$\label{thm:conditional} {\it Trademarks: Real Color and Ultra-Reliable \ DVI \ are \ trademarks \ of \ Genesis \ Microchip \ Inc.}$

### © Copyright 2002, Genesis Microchip Inc. All Rights Reserved.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to obtain the most recent revision of the document. Genesis Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors or omissions that may appear in this document.

### **Document history**

### **Previous publication releases:**

C5060-DAT-01A January 2001 C5060-DAT-01B February 2001 C5060-DAT-01C April 2001 C5060-DAT-01D April 2001 C5060-DAT-01E July 2001 C5060-DAT-01F November 2001

### **Current publication releases:**

| C5060-DAT-01G | Initial release | February 2002 |

|---------------|-----------------|---------------|

|---------------|-----------------|---------------|

# **Table Of Contents**

| 1. Overview                                                   | 1  |

|---------------------------------------------------------------|----|

| 1.1 gm5060 System Design Example                              | 2  |

| 1.2 gm5060/gm5060-H Features                                  | 3  |

| 2. Pinout Diagram                                             | 4  |

| 3. Pin List                                                   | 6  |

| 4. Functional Description                                     | 12 |

| 4.1 Clocking Options                                          | 13 |

| 4.1.1 TCLK Requirements                                       |    |

| 4.1.2 Synthesized Clocks                                      |    |

| 4.2 Hardware and Software Resets                              |    |

| 4.2.1 Hardware Reset                                          | 17 |

| 4.2.2 Software Reset                                          | 17 |

| 4.3 Analog to Digital Converter                               | 19 |

| 4.3.1 Pin Connection                                          | 19 |

| 4.3.2 ADC Characteristics                                     | 20 |

| 4.3.3 Sync. Signal Support                                    | 21 |

| 4.3.4 Clock Recovery                                          | 22 |

| 4.3.5 Sampling Phase Adjustment                               | 23 |

| 4.4 Ultra-Reliable Digital Visual Receiver (DVI Rx)           | 25 |

| 4.4.1 DVI Receiver Characteristics                            | 25 |

| 4.4.2 HDCP (High-Bandwidth Digital Content Protection System) | 26 |

| 4.5 ITU-R BT656 Video Input                                   | 27 |

| 4.5.1 YCbCr Input Clamping                                    | 27 |

| 4.6 Image Capture – Active Window Decoder                     | 28 |

| 4.6.1 ADC Capture Window                                      | 28 |

| 4.6.2 DVI Capture Window                                      | 30 |

| 4.6.3 ITU-R BT656 Capture Window                              | 30 |

| 4.7 Image Measurement                                         |    |

| 4.7.1 Input Format Measurement (IFM)                          |    |

| 4.7.2 Input Data Measurement                                  |    |

| 4.8 Digital Color Controls                                    |    |

| 4.8.1 YUV Hue / Saturation Controls                           |    |

| 4.8.2 RealColor Flesh tone Adjustment                         |    |

| 4.8.3 RGB Black Level / Contrast / Brightness                 |    |

| 4.8.4 Input Look-up Table                                     |    |

| 4.9 Horizontal Shrink                                         |    |

| 4.10 Frame Store Interface                                    |    |

| 4.10.1 Supported SDRAM Devices                                |    |

| 4.10.2 Adjustable Frame Store Interface Delays                | 40 |

| 4.10.3 Frame Store Bandwidth Requirements                                    | 40     |

|------------------------------------------------------------------------------|--------|

| 4.10.4 SDRAM Power On Sequence                                               | 41     |

| 4.10.5 SDRAM Power Down                                                      | 41     |

| 4.10.6 Pan and Crop Operations                                               | 41     |

| 4.10.7 Double Buffering Frame Store Bandwidth Requirements                   | 42     |

| 4.10.8 Freeze Frame                                                          | 42     |

| 4.10.9 Interlaced Formats and De-interlacing                                 | 42     |

| 4.11 Scaling                                                                 | 43     |

| 4.11.1 Pixel Replication Scaling                                             | 43     |

| 4.11.2 Vertical Shrink                                                       | 43     |

| 4.11.3 Adaptive Contrast Enhancement (ACE)                                   | 43     |

| 4.12 Gamma Correction LUT                                                    | 44     |

| 4.12.1 Gamma Correction                                                      | 44     |

| 4.12.2 Moiré Cancellation                                                    | 45     |

| 4.13 Display Timing and Control                                              | 46     |

| 4.13.1 Display Clock Generation – Display Digital Direct Synthesis Block (DD | DS) 46 |

| 4.13.2 Display Synchronization                                               | 47     |

| 4.13.3 Display Port Timing                                                   | 49     |

| 4.14 Data Path Bypass Options                                                | 51     |

| 4.15 OSD                                                                     | 53     |

| 4.15.1 Character Mapped OSD                                                  | 53     |

| 4.15.2 Bitmapped OSD                                                         | 59     |

| 4.15.3 Color Look-up Table (LUT)                                             | 59     |

| 4.15.4 Multiple OSD Windows                                                  | 59     |

| 4.15.5 OSD Stretch                                                           |        |

| 4.15.6 Blending                                                              | 59     |

| 4.15.7 OSD Merge                                                             |        |

| 4.16 On-Chip Microprocessor                                                  | 61     |

| 4.17 Bootstrap Configuration                                                 | 62     |

| 4.18 Host Interface                                                          | 63     |

| 4.18.1 2-wire Configuration                                                  | 63     |

| 4.18.2 6-Wire Configuration                                                  | 66     |

| 4.19 Miscellaneous Functions                                                 | 69     |

| 4.19.1 General Purpose Inputs and Outputs (GPIO's)                           | 69     |

| 4.19.2 Pulse Width Modulation (PWM) Back Light Control                       |        |

| 4.19.3 Low Power State                                                       | 69     |

| 5. Electrical Specifications                                                 | 70     |

| 5.1 DC Characteristics                                                       |        |

| 5.2 Preliminary AC Characteristics                                           |        |

| 6. Ordering Information                                                      |        |

|                                                                              |        |

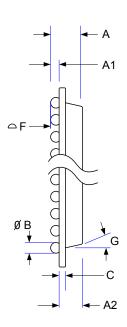

| 7. Mechanical Specifications                                                 | /7     |

# **List Of Tables**

| Table 1.  | ADC Signals                                         | 6  |

|-----------|-----------------------------------------------------|----|

| Table 2.  | DVI Receiver Signals                                | 6  |

| Table 3.  | RCLK and FCLK PLL Signals                           | 7  |

| Table 4.  | Video Input Port Signals                            | 7  |

| Table 5.  | Host Controller Interface Signals                   | 7  |

| Table 6.  | Display Port Signals                                | 8  |

| Table 7.  | Frame Store Interface Signals                       | 9  |

| Table 8.  | Power and Ground Signals                            | 11 |

| Table 9.  | No Connects                                         | 11 |

| Table 10. | Pin Connection for RGB Input with HSYNC/VSYNC       | 19 |

| Table 11. | ADC Characteristics                                 | 20 |

| Table 12. | DVI Receiver Characteristics                        | 25 |

| Table 13. | Framestore Bandwidth and Data Widths                | 41 |

| Table 14. | Bootstrap Signals                                   |    |

| Table 15. | Instruction Byte Map                                | 64 |

| Table 16. | Absolute Maximum Ratings (Both gm5060 and gm5060-H) | 70 |

| Table 17. | DC Characteristics                                  | 71 |

| Table 18. | Maximum Speed of Operation                          | 72 |

| Table 19. | ITU-R BT656 Input Port Timing                       | 74 |

| Table 20. | Framestore Output Timing and Adjustments            | 74 |

| Table 21. | Framestore Readback Timing (for all conditions)     | 74 |

| Table 22. | Display Timing and DCLK Adjustments                 | 75 |

| Table 23. | 2-Wire Host I/F Port Timing                         | 75 |

| Table 24. | 6-Wire Host I/F Port Timing                         | 75 |

# **List Of Figures**

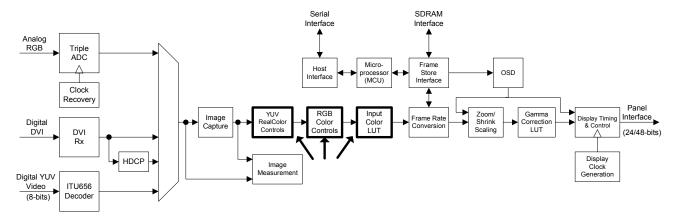

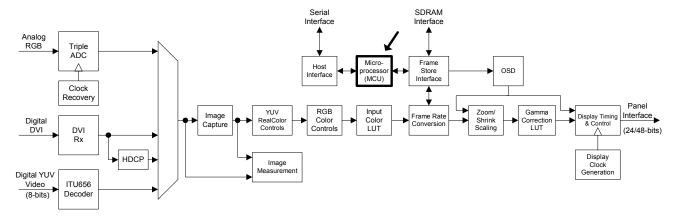

| Figure 1.  | gm5060 System Design Example                                            | 2  |

|------------|-------------------------------------------------------------------------|----|

| Figure 2.  | gm5060 Pinout Diagram                                                   | 5  |

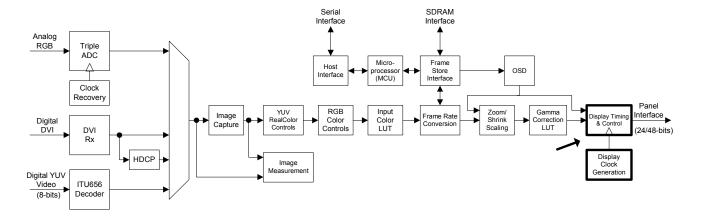

| Figure 3.  | gm5060 Functional Block Diagram                                         | 12 |

| Figure 4.  | TCLK connection (with Crystal Resonator)                                | 13 |

| Figure 5.  | TCLK parasitic capacitances                                             | 14 |

| Figure 6.  | TCLK connection (with Optional Resistor)                                | 15 |

| Figure 7.  | TCLK connection (with Oscillator)                                       | 15 |

| Figure 8.  | Internal Clock Sources                                                  | 16 |

| Figure 9.  | Hardware Reset                                                          | 18 |

| Figure 10. | ADC Block                                                               | 19 |

| Figure 11. | Example Signal Terminations                                             | 20 |

| Figure 12. | Positive and negative polarity OR-type CSYNC                            | 21 |

| Figure 13. | Positive and negative polarity XOR-type CSYNC                           | 21 |

| Figure 14. | Positive and negative polarity serration-type CSYNC                     | 22 |

| Figure 15. | Positive and negative polarity "serration with equalization"-type CSYNC | 22 |

| Figure 16. | gm5060 Clock Recovery                                                   | 23 |

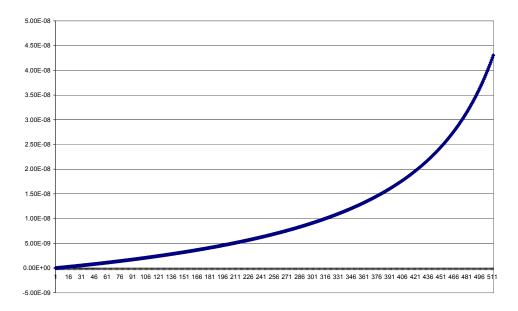

| Figure 17. | Phase Adjustment Delay Curve                                            | 24 |

| Figure 18. | DVI Block                                                               | 25 |

| Figure 19. | ITU-R BT656 Block                                                       | 27 |

| Figure 20. | Image Capture Block                                                     | 28 |

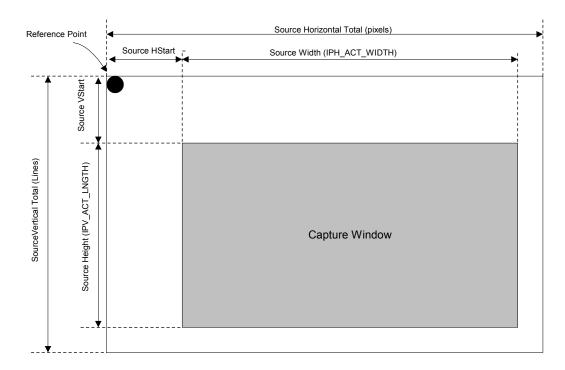

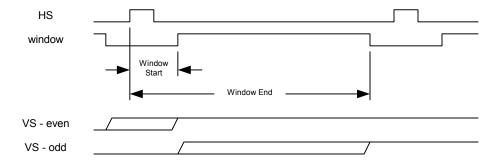

| Figure 21. | Capture Window                                                          | 29 |

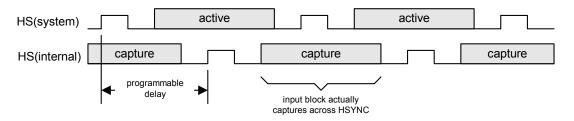

| Figure 22. | HSYNC Delay                                                             | 29 |

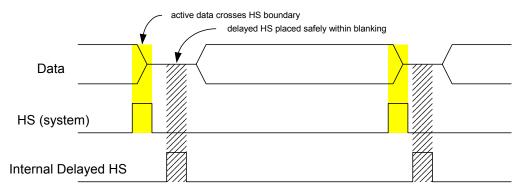

| Figure 23. | Active Data Crosses HSYNC Boundary                                      | 30 |

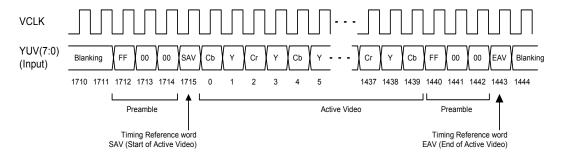

| Figure 24. | ITU-R BT656 Input                                                       | 31 |

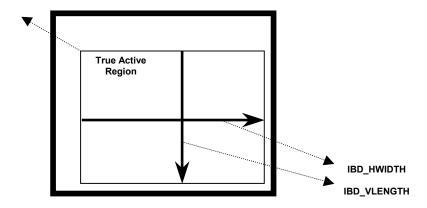

| Figure 25. | Image Measurement Block                                                 | 32 |

| Figure 26. | ODD/EVEN Field Detection                                                | 33 |

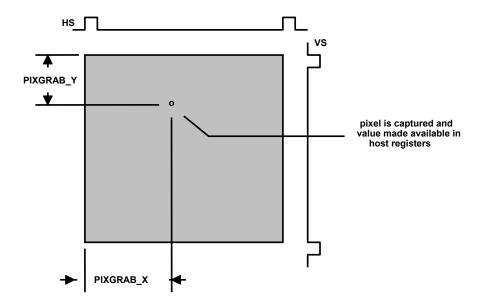

| Figure 27. | Pixel Grab                                                              | 35 |

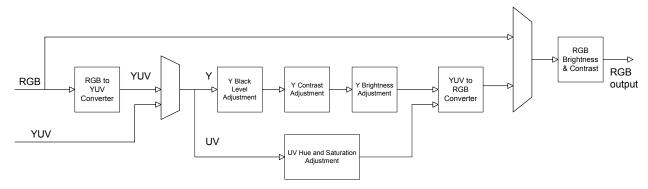

| Figure 28. | Digital Color Control Blocks                                            | 36 |

| Figure 29. | YUV Color Controls                                                      | 36 |

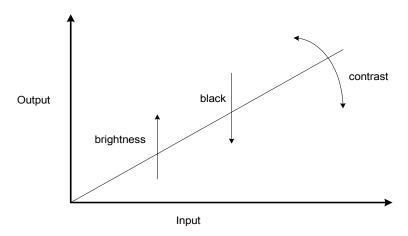

| Figure 30. | Black / Contrast / Brightness Transfer Function                         | 38 |

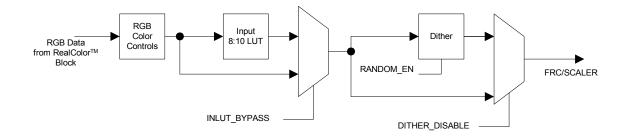

| Figure 31. | Input LUT and Dithering                                                 | 38 |

| Figure 32. | Frame Store Interface Blocks                                            | 40 |

| Figure 33. | FRC Required Parameters                                                 | 42 |

| Figure 34. | Scaling Block                                                           | 43 |

| Figure 35. | Gamma Correction LUT Block                                              | 44 |

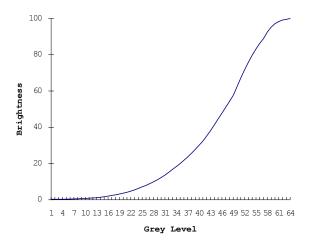

| Figure 36. | Gamma Response Curve                                                    | 45 |

| Figure 37. | Display Timing and Control Blocks                                       | 46 |

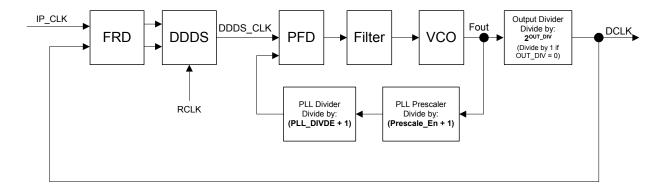

| Figure 38. | DDDS Block                                                              | 46 |

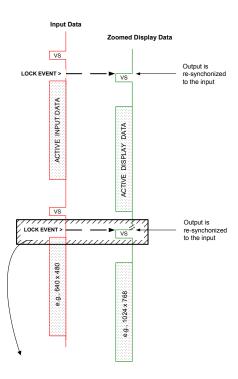

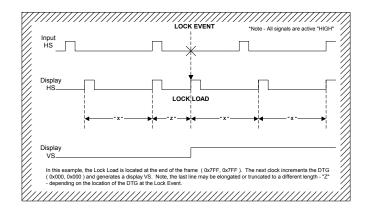

| Figure 39. | Lock Event Timing (Frame Sync Mode)                                     | 49 |

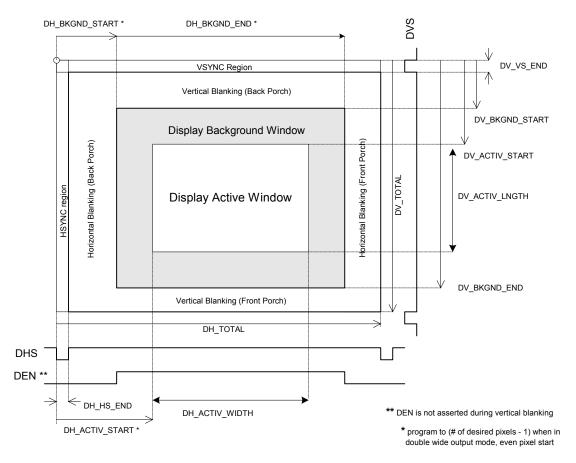

| Figure 40. | Display Windows and Timing                                              | 50 |

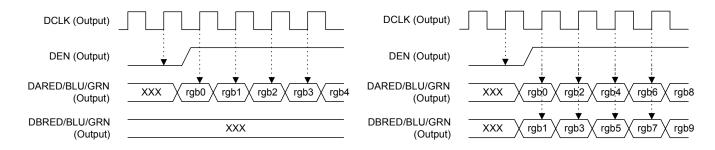

| Figure 41. | Single / Double-wide Display Data                                       |    |

| Figure 42. | Capture Only Mode                                                       |    |

| Figure 43. | FRC Bypass Mode                                                         |    |

| Figure 44. | Scaler Bypass Mode                                                      |    |

| Figure 45. | OSD Block                                                      | 53 |

|------------|----------------------------------------------------------------|----|

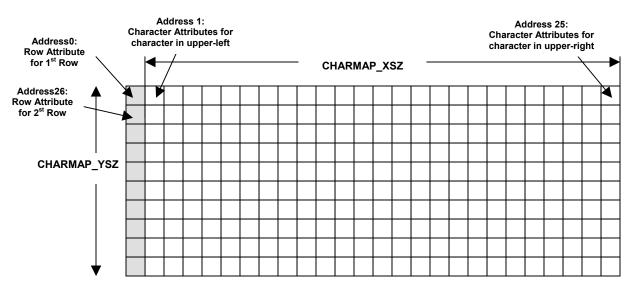

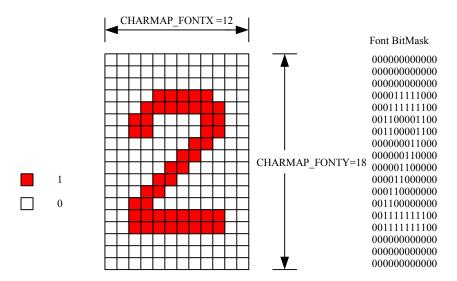

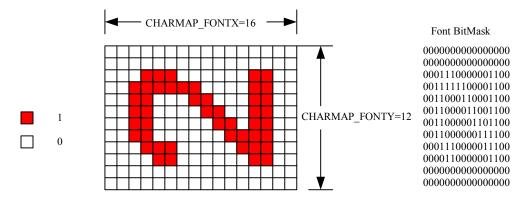

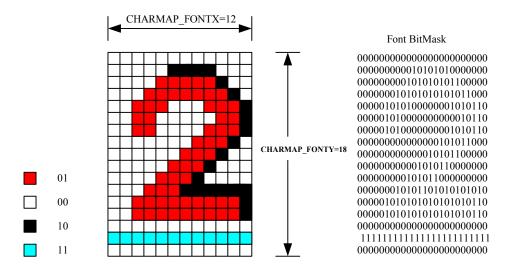

| Figure 46. | OSD Character Map                                              | 54 |

| Figure 47. | Non-Rotated SRAM Resident Font                                 | 56 |

| Figure 48. | Rotated SRAM Resident Font                                     | 57 |

| Figure 49. | User Define-able SRAM Resident Font                            | 57 |

| Figure 50. | MCU Block                                                      | 61 |

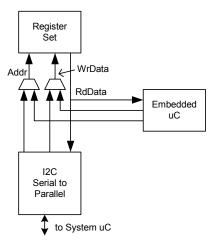

| Figure 51. | System μC - Embedded μC Communication                          | 61 |

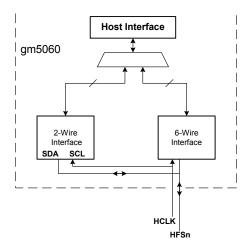

| Figure 52. | Host Interface Block                                           | 63 |

| Figure 53. | 2-Wire External Interface                                      | 63 |

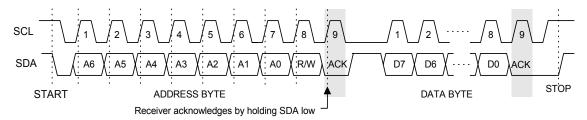

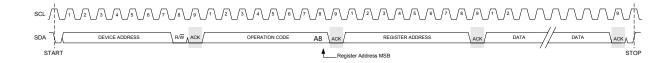

| Figure 54. | 2-wire Protocol Data Transfer                                  | 65 |

| Figure 55. | Write Address Increment and Write Address No Inc (0x10 & 0x20) | 65 |

| Figure 56. | Read Address Increment and Read Address No Inc (0x90 & 0xA0)   | 66 |

| Figure 57. | Direct Read                                                    | 66 |

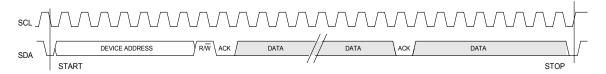

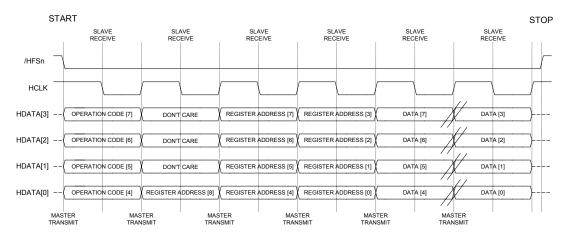

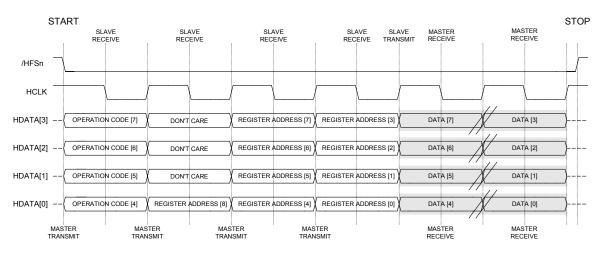

| Figure 58. | 6-Wire Write Operations (0x1x & 0x2x)                          | 68 |

| Figure 59. | 6-Wire Read Operations (0x9x & 0xAx)                           | 68 |

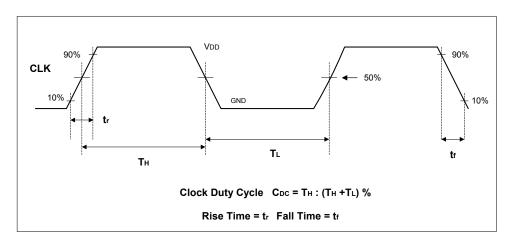

| Figure 60. | Clock Reference Levels                                         | 72 |

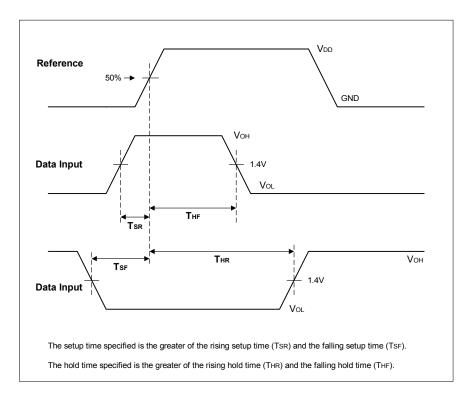

| Figure 61. | Setup and Hold Reference Levels                                | 73 |

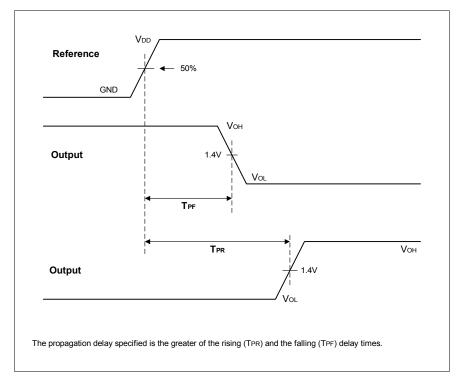

| Figure 62. | Propagation Delay Reference Levels                             | 73 |

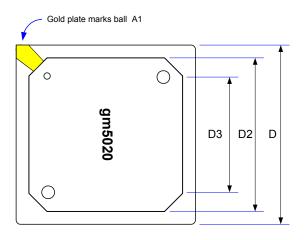

| Figure 63. | gm5060 292-pin PBGA                                            | 77 |

### 1. OVERVIEW

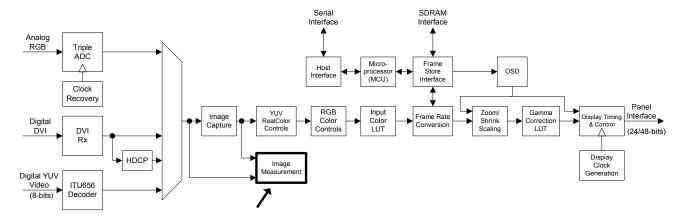

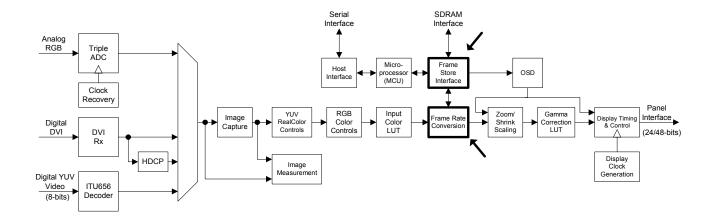

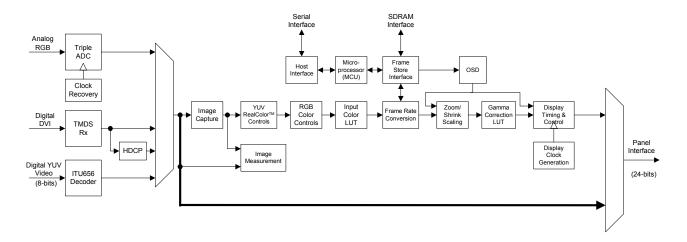

The gm5060 is a graphics processing IC providing high-quality images for LCD monitors and other pixelated displays. It combines a triple ADC, the Genesis Ultra-Reliable DVI™ receiver, a high quality zoom and shrink scaling engine, frame rate conversion, an on-screen display (OSD) controller, a microprocessor and many other functions in a single device. This high level of integration enables simple, flexible, cost-effective solutions featuring fewer required components.

The gm5060 is ideal for dual-interface (analog and digital) LCD monitors up to UXGA resolutions.

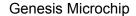

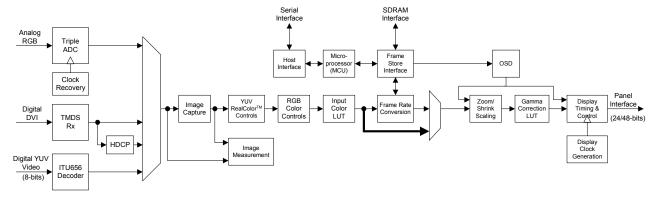

### 1.1 gm5060 System Design Example

Figure 1 below shows a typical dual interface LCD monitor system based on the gm5060. Designs based on the gm5060 have reduced system cost and simplified hardware and firmware design because only a minimal number of components are required in the system. The chip can be used in a variety of systems, ranging from 'single-chassis' solutions for XGA and UXGA monitors with frame store memory and video inputs. In addition, the gm5060 can be used in midrange SXGA monitors with no frame store memory.

Figure 1. gm5060 System Design Example

### 1.2 gm5060/gm5060-H Features

#### **FEATURES**

- Zoom and shrink scaling (all resolutions from VGA to UXGA)

- Frame rate conversion

- Integrated 8-bit triple-channel ADC / PLL

- Integrated Genesis Ultra-Reliable DVI <sup>™</sup> receiver (DVI 1.0)

- Integrated High-bandwidth Digital Content Protection (HDCP)

- · Embedded microcontroller simplifies OSD creation

- On-chip versatile OSD engine

- All system clocks synthesized from a single external crystal

- Programmable gamma correction (CLUT)

- Hue, Saturation, Brightness, Contrast and Gamma controls for RGB and YUV signals

- RealColor™ fleshtone adjustment

- PWM backlight intensity control

- 5 Volt tolerant inputs

#### High-Quality Advanced Scaling

- Fully programmable zoom/shrink ratios

- Independent horizontal / vertical zoom and shrink

- Variable sharpness control

- Moiré cancellation

#### Analog RGB Input Port

- Supports up to UXGA at 60Hz

- Support for Sync-on-Green (SOG) and Composite Sync modes

#### Ultra-Reliable DVI Receiver

- Single link on-chip DVI receiver

- Operating up to 165 MHz

- Direct connect to all DVI-compliant transmitters

- High-bandwidth Digital Content Protection (HDCP)

- Enhanced protection of HDCP secret keys

#### Digital Video Port

- 8-bit ITU-R BT656 input video

- Seamless connection to commercially available video capture devices

#### **APPLICATIONS**

- Multi-synchronous XGA, SXGA, or UXGA LCD monitors with dual analog/digital interface

- Any fixed-resolution pixelated display device

#### Auto-Configuration / Auto-Detection

- · Phase and image positioning

- Input format detection

- Compatibility with all graphic cards and standard VESA modes

#### Frame Store Interface

- Fully-programmable 48 / 32-bit wide data path

- Optional use of data compression for more flexibility and lower system solution cost

- Support for up to 143MHz SDRAM or SGRAM

#### On-chip OSD Controller

- Bit-mapped OSD capability

- On-chip RAM for downloadable fonts

- Horizontal and vertical stretch of OSD images

- Blinking, transparency and blending

#### Output Format

- Double wide up to UXGA 60Hz output

- Support for 8 or 6-bit panels (with high-quality dithering)

#### Operating Modes

- Frame rate conversion and scaling of images

- Bypass mode with no filtering and/or frame buffering

- 1:1 centering

- De-interlaced zoom

- Frame Sync and Free Run display synchronization modes

#### Highly Integrated Solution Provides Lowest System Cost

- Simplicity of Design Speeds Time to Market

- Complete reference design kit available (software and hardware)

#### **PACKAGE**

• 292-pin PBGA

# 2. PINOUT DIAGRAM

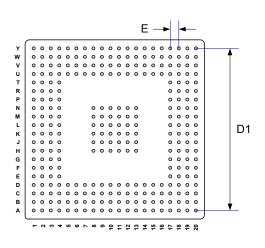

The gm5060 is available in a 292-pin PBGA (Ball Gate Array) package. Figure 2 below provides the ball locations for all signals.

### Power and Ground:

DGND Periphery and Core Digital Ground

DVDD\_3.3 Periphery Digital VDD (3.3V supply)

DVDD\_2.5 Core Digital VDD (2.5V supply)

PGND PLL Ground

PLLVDD\_3.3 PLL VDD (3.3V supply)

AGND Analog Ground

AVDD\_3.3 Analog VDD (3.3V supply)

AVDD\_2.5 Analog VDD (2.5V supply)

### Pinout Legend:

DVI

High Frequency Clock

ADC

DDS and PLL

Figure 2. gm5060 Pinout Diagram

|          | ⋖          | Ф          | ပ        | Ω        | ш        | ш          | G                  | I          | 7          | ¥        | _        | Σ            | Z            | ۵          | <b>~</b>       | <b>—</b> | <b>-</b>   | >         | <b>≥</b>  | >         |

|----------|------------|------------|----------|----------|----------|------------|--------------------|------------|------------|----------|----------|--------------|--------------|------------|----------------|----------|------------|-----------|-----------|-----------|

| 20       | DBGRN2     | DBGRN0     | DBBLU6   | DBBLU3   | DBBLU0   | DHS        | DCLK               | DARED4     | DARED1     | DAGRN6   | DAGRN5   | DAGRN2       | DABLU7       | DABLU4     | DABLU1         | FSDATA46 | FSDATA43   | FSDATA40  | FSDATA38  | FSDATA37  |

| 19       | DBGRN3     | DBGRN1     | DBBLU7   | DBBLU4   | DBBLU1   | DVS        | GPIO7 / DOVL       | DARED5     | DARED2     | DAGRN7   | DAGRN4   | DAGRN1       | DABLU6       | DABLU3     | DABLU0         | FSDATA45 | FSDATA42   | FSDATA39  | FSDATA36  | FSDATA35  |

| 18       | DBGRN6     | DBGRN5     | DBGRN4   | DBBLU5   | DBBLU2   | DEN        | GPIO6 /<br>DFSYNCn | DARED6     | DARED3     | DAREDO   | DAGRN3   | DAGRN0       | DABLU5       | DABLU2     | FSDATA47       | FSDATA44 | FSDATA41   | FSDATA34  | FSDATA33  | FSDATA32  |

| 17       | DBRED1     | DBRED0     | DBGRN7   | DVDD_2.5 | DVDD_3.3 | DVDD_2.5   | DVDD_3.3           | DARED7     | DVDD_3.3   | DVDD_2.5 | DVDD_3.3 | DVDD_2.5     | DVDD_3.3     | DVDD_2.5   | DVDD_3.3       | DVDD_2.5 | DVDD_3.3   | FSDATA31  | FSDATA30  | FSDATA29  |

| 16       | DBRED4     | DBRED3     | DBRED2   | DVDD_3.3 |          |            |                    |            |            |          |          |              |              |            |                |          | DVDD_2.5   | FSDATA28  | FSDATA27  | FSDATA26  |

| 15       | DBRED7     | DBRED6     | DBRED5   | DVDD_3.3 |          |            |                    |            |            |          |          |              |              |            |                |          | DVDD_3.3   | FSDATA25  | FSDATA24  | FSDATA23  |

| 4        | YUV2       | YUV1       | YUV0     | DVDD_2.5 |          |            |                    |            |            |          |          |              |              |            |                |          | DVDD_2.5   | FSDATA22  | FSDATA21  | FSDATA20  |

| 13       | YUV5       | YUV4       | YUV3     | DVDD_3.3 |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_3.3   | FSDATA19  | FSDATA18  | FSDATA17  |

| 12       | VCLK       | YUV7       | VUV6     | DVDD_2.5 |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_3.3   | FSDQM2    | FSDQM3    | FSDATA16  |

| 7        | AVDD_2.5   | AVDD_3.3   | AGND     | AGND     |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_2.5   | FSDATA15  | FSDATA14  | FSDATA13  |

| 10       | AVDD_2.5   | REXT       | RX2+     | RX2-     |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_3.3   | FSDATA10  | FSDATA11  | FSDATA12  |

| 6        | AVDD_2.5   | AVDD_3.3   | RX1+     | RX-1     |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_2.5   | FSDATA7   | FSDATA8   | FSDATA9   |

| <b>∞</b> | AVDD_2.5   | AVDD_3.3   | RX0+     | RX0-     |          |            |                    | DGND       | DGND       | DGND     | DGND     | DGND         | DGND         |            |                |          | DVDD_3.3   | FSDATA6   | FSDQM0    | FSDQM1    |

| ^        | 5 AVDD_2.5 | 3 AVDD_3.3 | AGND     | AGND     |          |            |                    |            |            |          |          |              |              |            |                |          | 3 DVDD_2.5 | FSDATA3   | FSDATA4   | FSDATA5   |

| 9        | AVDD_2.5   | AVDD_3.3   | RXC+     | RXC-     |          |            |                    |            |            |          |          |              |              |            |                |          | 3 DVDD_3.3 | 2 FSDATA0 | 1 FSDATA1 | D FSDATA2 |

| ß        | N/C        | N/C        | AGND     | AGND     |          |            |                    |            |            |          |          |              |              |            | 89             |          | DVDD_3.3   | FSADDR2   | FSADDR1   | FSADDR0   |

| 4        | AGND       | AGND       | AGND     | AGND     | AGND     | PLLVDD_3.3 | PLLGND             | XTAL       | TCLK       | DVDD_2.5 | DVDD_3.3 | GPIO1 / PWM1 | DVDD_2.5     | HDATA2     | IRQINn / GPIO8 | DVDD_3.3 | DVDD_2.5   | FSADDR5   | FSADDR4   | FSADDR3   |

| က        | AGND       | AGND       | AVDD_3.3 | AVDD_3.3 | AVDD_3.3 | PLLGND     | PLLVDD_3.3         | PLLGND     | PLLVDD_3.3 | PLLGND   | EXTCLK   | GPI02        | DDC_SDA      | HDATA3     | IRQn           | FSCLK    | FSCAS      | FSADDR8   | FSADDR7   | FSADDR6   |

| 7        | AGND       | AVDD_3.3   | BLUE-    | GREEN+   | RED-     | PLLVDD_3.3 | PLLGND             | PLLGND     | PLLGND     | N/C      | HSYNC    | GP103        | DDC_SCL      | HFSn / SDA | HDATA0         | DGND     | FSWE       | FSADDR13  | FSADDR10  | FSADDR9   |

| ~        | N/C        | AGND       | BLUE+    | GREEN-   | RED+     | N/C        | PLLVDD_3.3         | PLLVDD_3.3 | PLLVDD_3.3 | VSYNC    | GPIO5    | GPIO4        | GPIO0 / PWM0 | HCLK / SCL | нрата1         | RESETn   | FSCKE      | FSRAS     | FSADDR12  | FSADDR11  |

|          | 4          | Ш          | ပ        | Ω        | ш        | ш          | G                  | I          | 7          | ¥        | _        | Σ            | z            | ۵          | <b>~</b>       | $\vdash$ | $\supset$  | >         | ≥         | >         |

# 3. PIN LIST

I/O Legend: I = Input O = Output P = Power G= Ground

### Table 1. ADC Signals

| Name   | I/O | Ball# | Description                                                                                                                                                                                                                                                                              |

|--------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REXT   | I   | B10   | External termination resistor. A 1% 1K ohm resistor must be connected from this pin to AVDD_3.3 (3.3V analog power supply). This termination resistor determines current references for both the DVI receiver block and Analog HSYNC Delay block for both DVI and analog configurations. |

| RED+   | I   | E1    | Positive analog input for Red channel.                                                                                                                                                                                                                                                   |

| RED-   | I   | E2    | Negative analog input for Red channel.                                                                                                                                                                                                                                                   |

| GREEN+ | I   | D2    | Positive analog input for Green channel.                                                                                                                                                                                                                                                 |

| GREEN- | I   | D1    | Negative analog input for Green channel.                                                                                                                                                                                                                                                 |

| BLUE+  | I   | C1    | Positive analog input for Blue channel.                                                                                                                                                                                                                                                  |

| BLUE-  | I   | C2    | Negative analog input for Blue channel.                                                                                                                                                                                                                                                  |

| HSYNC  | I   | L2    | ADC input horizontal sync or composite sync input.                                                                                                                                                                                                                                       |

|        |     |       | [Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                                                                                                         |

| VSYNC  | Ι   | K1    | ADC input vertical sync.                                                                                                                                                                                                                                                                 |

|        |     |       | [Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                                                                                                         |

### Table 2. DVI Receiver Signals

| Name    | I/O | Ball# | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REXT    | I   | B10   | External termination resistor. A 1% 1K ohm resistor must be connected from this pin to AVDD_3.3 (3.3V analog power supply). This termination resistor determines current references for both the DVI receiver block and Analog HSYNC Delay block for both DVI and analog configurations.                                                                                                                               |

| RX2+    | I   | C10   | DVI input channel 2 positive component; RED data and embedded CTL3                                                                                                                                                                                                                                                                                                                                                     |

| RX2-    | I   | D10   | DVI input channel 2 negative component; RED data and embedded CTL3                                                                                                                                                                                                                                                                                                                                                     |

| RX1+    | I   | C9    | DVI input channel 1 positive component; GREEN data                                                                                                                                                                                                                                                                                                                                                                     |

| RX1-    | I   | D9    | DVI input channel 1 negative component; GREEN data                                                                                                                                                                                                                                                                                                                                                                     |

| RX0+    | I   | C8    | DVI input channel 0 positive component; BLUE data                                                                                                                                                                                                                                                                                                                                                                      |

| RX0-    | I   | D8    | DVI input channel 0 negative component; BLUE data                                                                                                                                                                                                                                                                                                                                                                      |

| RXC+    | I   | C6    | DVI input clock positive component                                                                                                                                                                                                                                                                                                                                                                                     |

| RXC-    | Ι   | D6    | DVI input clock negative component                                                                                                                                                                                                                                                                                                                                                                                     |

| DDC_SCL | I   | N2    | For the gm5060-H (HDCP-enabled), this pin is used for DDC Interface for DVI-HDCP communication. This is SCL for slave-only DDC communication.  [Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]  For the gm5060 (non-HDCP), this pin is an unused CMOS input that may be left unconnected. However, it is preferred that this pin be connected to a known logic state.                                 |

| DDC_SDA | Ю   | N3    | For the gm5060-H (HDCP-enabled), this pin is used for DDC Interface for DVI-HDCP communication. This is SDA for slave-only DDC communication.  [Bidirectional, 4mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant]  For the gm5060 (non-HDCP), this pin is an unused CMOS input that may be left unconnected. However, it is preferred that this pin be connected to a known logic state. |

### Table 3. RCLK and FCLK PLL Signals

| Name | I/O | Ball# | Description                                                                                                                                             |

|------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK | О   | J4    | Feedback connection to crystal. If the reference clock source is a clock oscillator, this pin should be grounded through a 2.7K pulldown resistor.      |

| XTAL | I   | H4    | Crystal/oscillator input. For crystal, the frequency restrictions are: Min = 14MHz Max = 50MHz. For oscillator, Min = 14 MHz, Max = 24 MHz [3.3V level] |

### Table 4. Video Input Port Signals

| Name | I/O | Ball# | Description                                                                                            |

|------|-----|-------|--------------------------------------------------------------------------------------------------------|

| VCLK | I   | A12   | Input sample clock (27MHz) from video decoder. [Input, 5V-tolerant]                                    |

| YUV7 | I   | B12   | Input YUV data in ITU-R BT656 format with embedded SAV and EAV.                                        |

| YUV6 |     | C12   | These inputs feature internal pull-downs. Any external pull-ups used on these inputs should not exceed |

| YUV5 |     | A13   | 10k ohms. Larger values run the risk of lowering the input high voltage to a value that would create   |

| YUV4 |     | B13   | large currents in the input pads.                                                                      |

| YUV3 |     | C13   | YUV(7:0) incorporate General Purpose Inputs (GPIs). See Section 4.19.1.                                |

| YUV2 |     | A14   | [Input, 100KΩ pull-down, 5V-tolerant]                                                                  |

| YUV1 |     | B14   |                                                                                                        |

| YUV0 |     | C14   |                                                                                                        |

### Table 5. Host Controller Interface Signals

| Name           | I/O | Ball# | Description                                                                                            |

|----------------|-----|-------|--------------------------------------------------------------------------------------------------------|

| HCLK / SCL     | I   | P1    | Host Protocol input clock. HCLK for 6-wire nibble, SCL for 2-wire mode.                                |

|                |     |       | [Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                       |

| HFSn / SDA     | IO  | P2    | Host Protocol framing signal for 6-wire nibble mode. Also used as SDA (open drain) signal for 2-wire   |

|                |     |       | mode. [Bidirectional, 4mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant] |

| HDATA3         | IO  | Р3    | Host Protocol data nibble for 6-wire mode. The upper nibble byte(3:0) is transferred first followed by |

| HDATA2         |     | P4    | lower nibble byte(7:4).                                                                                |

| HDATA1         |     | R1    | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant]       |

| HDATA0         |     | R2    |                                                                                                        |

| IRQn           | О   | R3    | Interrupt output pin. May be active drive (active low) or open drain. [8mA drive, 5V-tolerant]         |

| IRQINn / GPIO8 | IO  | R4    | Interrupt input to internal 8051 OCM is active low. OCM interrupt#0. This signal is also GPIO8.        |

|                |     |       | Always open drain when in GPO mode.                                                                    |

|                |     |       | [Bidirectional, schmitt trigger input (400mV typical hysteresis), 5V-tolerant, 8mA drive output]       |

| RESETn         | I   | T1    | Hardware Reset signals is active low.                                                                  |

|                |     |       | [Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                       |

| EXTCLK         | I   | L3    | External clock. For test purposes only when Display DDS is unused. [Input, 5V-tolerant]                |

| GPIO0 / PWM0   | IO  | N1    | General purpose input/output signal or PWM0. Open drain option via register bit.                       |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

| GPIO1 / PWM1   | IO  | M4    | General purpose input/output signal or PWM1. Open drain option via register bit.                       |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

| GPIO2          | IO  | M3    | General purpose input/output signals. Open drain option via register bit.                              |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

| GPIO3          | IO  | M2    | General purpose input/output signals. Open drain option via register bit.                              |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

| GPIO4          | IO  | M1    | General purpose input/output signals. Open drain option via register bit.                              |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

| GPIO5          | IO  | L1    | General purpose input/output signals. Open drain option via register bit.                              |

|                |     |       | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]       |

February 2002 7 C5060-DAT-01G

Table 6. Display Port Signals

| Name             | I/O | Ball#      | Description                                                                                                  |

|------------------|-----|------------|--------------------------------------------------------------------------------------------------------------|

| GPIO6 / DFSYNCn  | IO  | G18        | GPIO6 by default. Open drain GPO option via register bit.                                                    |

|                  |     |            | If DFSYNCn is register bit enabled, manual synchronization of display timing causes display timing to        |

|                  |     |            | jump to its H and V lock load location.                                                                      |

|                  |     |            | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]             |

| GPIO7 / DOVL     | IO  | G19        | GPIO7 by default. Open drain GPO option via register bit.                                                    |

|                  |     |            | If DOVL is register bit enabled, overlay valid display pixels are indicated by active DOVL.                  |

|                  |     |            | [Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]             |

| DCLK             | О   | G20        | Display output clock. [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                         |

| DVS              | О   | F19        | Display vertical sync. [default = active high]                                                               |

|                  |     |            | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DHS              | О   | F20        | Display horizontal sync. [default = active high]                                                             |

|                  |     |            | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DEN              | О   | F18        | Display Enable frames the output background window.                                                          |

|                  |     |            | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DARED7           | О   | H17        | Display output red data (even or left pixel).                                                                |

| DARED6           |     | H18        | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DARED5           |     | H19        |                                                                                                              |

| DARED4           |     | H20        |                                                                                                              |

| DARED3           |     | J18        |                                                                                                              |

| DARED2           |     | J19        |                                                                                                              |

| DARED1           |     | J20        |                                                                                                              |

| DARED0           |     | K18        |                                                                                                              |

| DAGRN7           | О   | K19        | Display output green data (even or left pixel).                                                              |

| DAGRN6           |     | K20        | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DAGRN5           |     | L20        |                                                                                                              |

| DAGRN4           |     | L19        |                                                                                                              |

| DAGRN3           |     | L18        |                                                                                                              |

| DAGRN2           |     | M20        |                                                                                                              |

| DAGRN1           |     | M19        |                                                                                                              |

| DAGRN0           |     | M18        |                                                                                                              |

| DABLU7           | О   | N20        | Display output blue data (even or left pixel).                                                               |

| DABLU6           |     | N19        | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DABLU5           |     | N18        |                                                                                                              |

| DABLU4           |     | P20        |                                                                                                              |

| DABLU3           |     | P19        |                                                                                                              |

| DABLU2<br>DABLU1 |     | P18        |                                                                                                              |

|                  |     | R20        |                                                                                                              |

| DABLU0           |     | R19        | Display output and data (add on right mixel)                                                                 |

| DBRED4           | О   | A15<br>B15 | Display output red data (odd or right pixel).  [Tri state output programmable drive 0.24mA, not 5V televent] |

| DBRED6<br>DBRED5 |     | C15        | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DBRED4           |     | A16        |                                                                                                              |

| DBRED3           |     | B16        |                                                                                                              |

| DBRED2           |     | C16        |                                                                                                              |

| DBRED1           |     | A17        |                                                                                                              |

| DBRED0           |     | B17        |                                                                                                              |

| DBGRN7           | 0   | C17        | Display output green data (odd or right pixel).                                                              |

| DBGRN6           |     | A18        | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]                                               |

| DBGRN5           |     | B18        | [ ome output, programmation arrive of 2 min i, not 5 + toterant]                                             |

| DBGRN4           |     | C18        |                                                                                                              |

| Name   | I/O | Ball# | Description                                                    |

|--------|-----|-------|----------------------------------------------------------------|

| DBGRN3 |     | A19   |                                                                |

| DBGRN2 |     | A20   |                                                                |

| DBGRN1 |     | B19   |                                                                |

| DBGRN0 |     | B20   |                                                                |

| DBBLU7 | О   | C19   | Display output blue data (odd or right pixel).                 |

| DBBLU6 |     | C20   | [Tri-state output, programmable drive 0-24mA, not 5V-tolerant] |

| DBBLU5 |     | D18   |                                                                |

| DBBLU4 |     | D19   |                                                                |

| DBBLU3 |     | D20   |                                                                |

| DBBLU2 |     | E18   |                                                                |

| DBBLU1 |     | E19   |                                                                |

| DBBLU0 |     | E20   |                                                                |

### Table 7. Frame Store Interface Signals

|          |     |       | Tuble 7. Traine otore interrace digitals                                                       |

|----------|-----|-------|------------------------------------------------------------------------------------------------|

| Name     | I/O | Ball# | Description                                                                                    |

| FSCLK    | О   | Т3    | SDRAM clock. This signal is rising edge active.                                                |

|          |     |       | [Tri-state output, Programmable Drive 0-24mA, not 5V-tolerant]                                 |

| FSCKE    | О   | U1    | SDRAM clock enable. This signal is active high.                                                |

|          |     |       | [Tri-state output, 8mA drive, 5V-tolerant]                                                     |

| FSRAS    | О   | V1    | SDRAM row address strobe. This signal is active low                                            |

|          |     |       | [Tri-state output, 8mA drive, 5V-tolerant]                                                     |

| FSCAS    | О   | U3    | SDRAM column address strobe. This signal is active low.                                        |

|          |     |       | [Tri-state output, 8mA drive, 5V-tolerant]                                                     |

| FSWE     | О   | U2    | SDRAM write enable. This signal is active low.                                                 |

|          |     |       | [Tri-state output, 8mA drive, 5V-tolerant]                                                     |

| FSDQM3   | О   | W12   | SDRAM data masks. Each bit enables one of four SDRAM byte "lanes". This allows host OSD access |

| FSDQM2   |     | V12   | to the SDRAM to be byte oriented. This signal is active high.                                  |

| FSDQM1   |     | Y8    | Bit 0 enables FSDATA(7:0).                                                                     |

| FSDQM0   |     | W8    | Bit 1 enables FSDATA(15:8).                                                                    |

|          |     |       | Bit 2 enables FSDATA(23:16).                                                                   |

|          |     |       | Bit 3 enables FSDATA(31:24).                                                                   |

|          |     |       | [Tri-state output, 8mA drive, 5V-tolerant]                                                     |

| FSADDR13 | IO  | V2    | SDRAM multiplexed address bus.                                                                 |

| FSADDR12 |     | W1    | FSADDR[13:0] are used for bootstrapping configuration. See Section 4.17.                       |

| FSADDR11 |     | Y1    | [Bidirectional, 8mA drive output, 5V-tolerant]                                                 |

| FSADDR10 |     | W2    |                                                                                                |

| FSADDR9  |     | Y2    |                                                                                                |

| FSADDR8  |     | V3    |                                                                                                |

| FSADDR7  |     | W3    |                                                                                                |

| FSADDR6  |     | Y3    |                                                                                                |

| FSADDR5  |     | V4    |                                                                                                |

| FSADDR4  |     | W4    |                                                                                                |

| FSADDR3  |     | Y4    |                                                                                                |

| FSADDR2  |     | V5    |                                                                                                |

| FSADDR1  |     | W5    |                                                                                                |

| FSADDR0  |     | Y5    |                                                                                                |

| FSDATA47 | IO | R18 | SDRAM data bus. Optionally programmable to 48 or 32 bits wide. Default is 32 bits wide. |

|----------|----|-----|-----------------------------------------------------------------------------------------|

| FSDATA46 |    | T20 | [Bidirectional, 8mA drive output, 100KΩ pull-down, 5V-tolerant]                         |

| FSDATA45 |    | T19 |                                                                                         |

| FSDATA44 |    | T18 |                                                                                         |

| FSDATA43 |    | U20 |                                                                                         |

| FSDATA42 |    | U19 |                                                                                         |

| FSDATA41 |    | U18 |                                                                                         |

| FSDATA40 |    | V20 |                                                                                         |

| FSDATA39 |    | V19 |                                                                                         |

| FSDATA38 |    | W20 |                                                                                         |

| FSDATA37 |    | Y20 |                                                                                         |

| FSDATA36 |    | W19 |                                                                                         |

| FSDATA35 |    | Y19 |                                                                                         |

| FSDATA34 |    | V18 |                                                                                         |

| FSDATA33 |    | W18 |                                                                                         |

| FSDATA32 |    | Y18 |                                                                                         |

| FSDATA31 |    | V17 |                                                                                         |

| FSDATA30 |    | W17 |                                                                                         |

| FSDATA29 |    | Y17 |                                                                                         |

| FSDATA28 |    | V16 |                                                                                         |

| FSDATA27 |    | W16 |                                                                                         |

| FSDATA26 |    | Y16 |                                                                                         |

| FSDATA25 |    | V15 |                                                                                         |

| FSDATA24 |    | W15 |                                                                                         |

| FSDATA23 |    | Y15 |                                                                                         |

| FSDATA22 |    | V14 |                                                                                         |

| FSDATA21 |    | W14 |                                                                                         |

| FSDATA20 |    | Y14 |                                                                                         |

| FSDATA19 |    | V13 |                                                                                         |

| FSDATA18 |    | W13 |                                                                                         |

| FSDATA17 |    | Y13 |                                                                                         |

| FSDATA16 |    | Y12 |                                                                                         |

| FSDATA15 |    | V11 |                                                                                         |

| FSDATA14 |    | W11 |                                                                                         |

| FSDATA13 |    | Y11 |                                                                                         |

| FSDATA12 |    | Y10 |                                                                                         |

| FSDATA11 |    | W10 |                                                                                         |

| FSDATA10 |    | V10 |                                                                                         |

| FSDATA9  |    | Y9  |                                                                                         |

| FSDATA8  |    | W9  |                                                                                         |

| FSDATA7  |    | V9  |                                                                                         |

| FSDATA6  |    | V8  |                                                                                         |

| FSDATA5  |    | Y7  |                                                                                         |

| FSDATA4  |    | W7  |                                                                                         |

| FSDATA3  |    | V7  |                                                                                         |

| FSDATA2  |    | Y6  |                                                                                         |

| FSDATA1  |    | W6  |                                                                                         |

| FSDATA0  |    | V6  |                                                                                         |

Table 8. Power and Ground Signals

| <b>Group Name</b> | I/O | Ball #                                                                                                                                      | Description                                             |

|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| PLLGND            | G   | F3, G2, G4, H2, H3, J2, K3                                                                                                                  | Analog PLL / DDS Ground                                 |

| PLLVDD_3.3        | P   | F2, F4, G1, G3, H1, J1, J3                                                                                                                  | Analog PLL / DDS 3.3VDC Bypass to PLLGND (0.1uF)        |

| AGND              | G   | A2, A3, A4, B1, B3, B4, C4, C5, C7, C11, D4, D5, D7, D11, E4                                                                                | Analog Ground                                           |

| AVDD_2.5          | P   | A6, A7, A8, A9, A10, A11                                                                                                                    | Analog 2.5VDC Supply Bypass to AGND (0.1uF)             |

| AVDD_3.3          | P   | B2, B6, B7, B8, B9, B11, C3, D3, E3                                                                                                         | Analog 3.3VDC Supply Bypass to AGND (0.1uF)             |

| DGND              | G   | H8, H9, H10, H11, H12, H13, J8, J9, J10, J11, J12, J13, K8, K9, K10, K11, K12, K13, L8, L9, L10, L11, L12, L13, M8, M9, M10, M11, M12, M13, | Digital Ground (Periphery and Core Logic)               |

|                   |     | N8, N9, N10, N11, N12, N13, T2                                                                                                              |                                                         |

| DVDD_2.5          | P   | D17, D14, D12, F17, K4, K17, M17, N4, P17, T17, U4, U7, U9, U11, U14, U16                                                                   | Digital VDD, 2.5VDC (Core Logic. Bypass to DGND, 0.1uF) |

| DVDD_3.3          | P   | D16, D15, D13, E17, G17, J17, L4, L17, N17, R17, T4, U5, U6, U8, U10, U12, U13, U15, U17                                                    | Digital VDD, 3.3VDC (I/O pins. Bypass to DGND, 0.1uF)   |

Table 9. No Connects

| <b>Group Name</b> | I/O | Ball #             | Description                            |  |  |

|-------------------|-----|--------------------|----------------------------------------|--|--|

| N/C               | -   | A1, A5, B5, F1, K2 | No Connect. Leave these pins floating. |  |  |

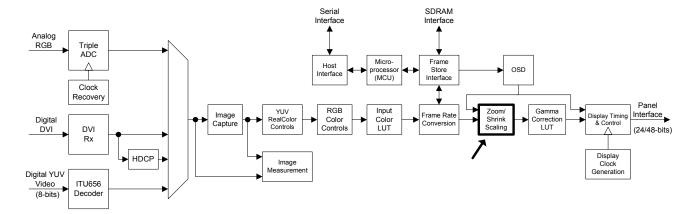

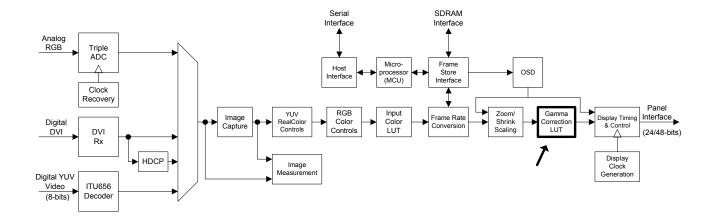

# 4. FUNCTIONAL DESCRIPTION

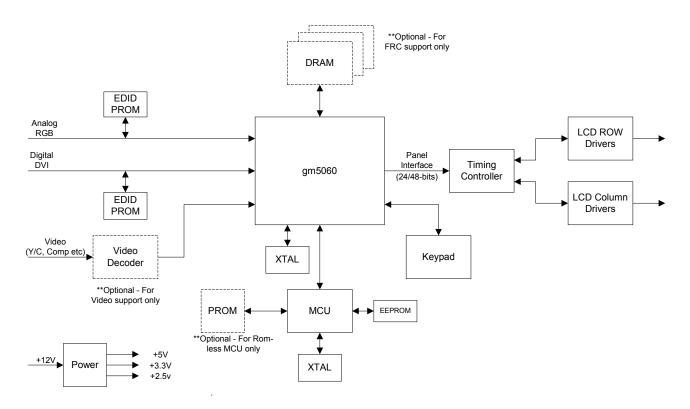

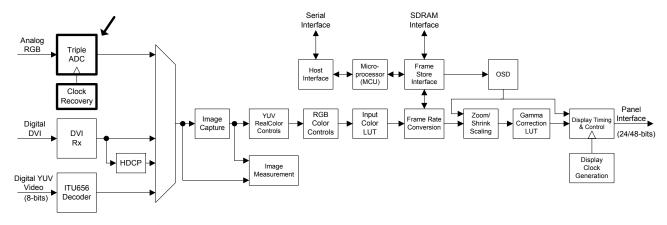

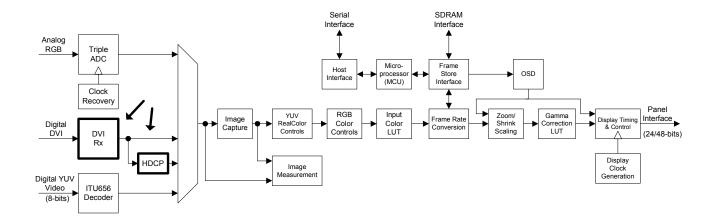

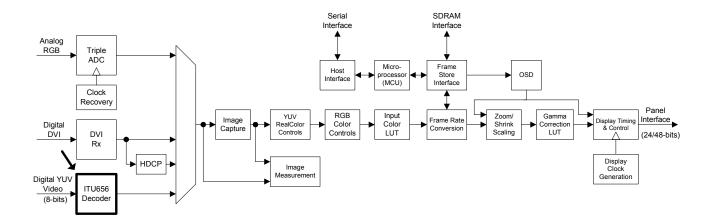

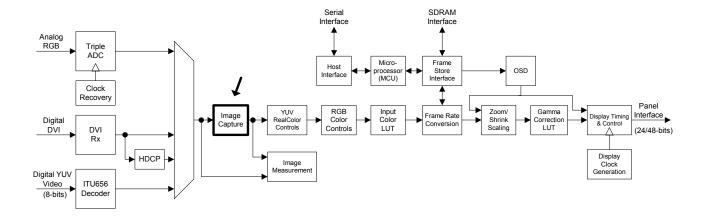

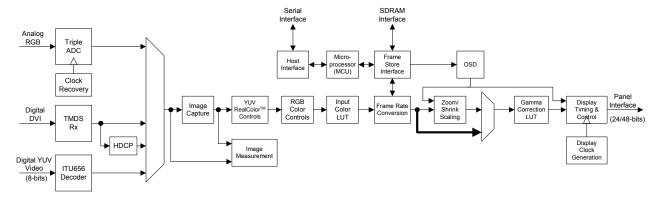

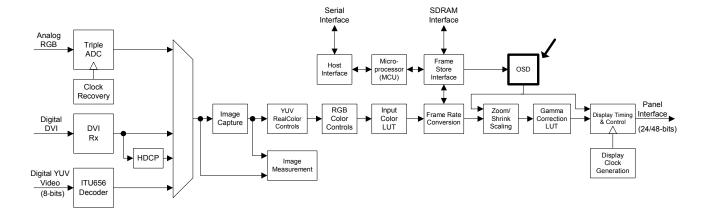

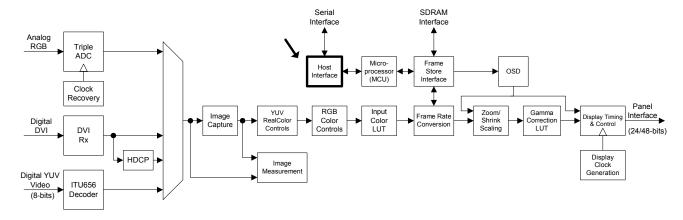

A functional block diagram is illustrated below. Each of the functional units shown is described in the following sections.

Figure 3. gm5060 Functional Block Diagram

### **4.1 Clocking Options**

The gm5060 features four clock inputs:

- 1) <u>Timing Clock (TCLK)</u>. This is a required clock used as a reference frequency source for the gm5060. Additional clocks are synthesized internally using this reference. TCLK may be connected to a crystal resonator or external oscillator and is further described below.

- 2) DVI Differential Input Clock (RC+ and RC-). Provided by the external DVI interface.

- 3) Video Clock (VCLK) input pin. Provided by the external video decoder.

- 4) <u>Host Interface Transfer Clock</u> (HCLK for 6-Wire nibble; SCL for 2-wire serial). Provided by the external micro controller (MCU).

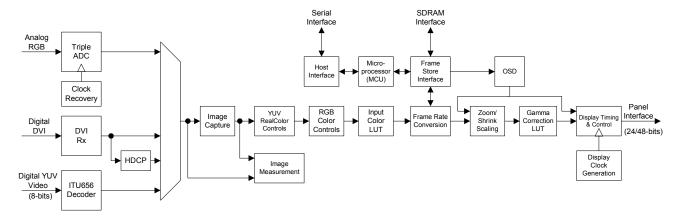

#### **4.1.1 TCLK Requirements**

The TCLK may be generated using either a crystal resonator circuit (recommended) or an external clock oscillator. The TCLK frequency should range between 14 and 50 MHz, though 24 MHz is preferred.

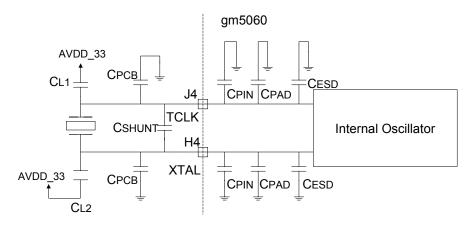

If TCLK is derived from a crystal resonator, an internal oscillator circuit generates a very low jitter and low harmonic clock within the gm5060. The crystal should be connected between the XTAL and TCLK pins and utilize appropriately sized loading capacitors.  $C_{L1}$  and  $C_{L2}$  are terminated to AVDD\_33 to increase the power supply rejection ratio. This is shown in the diagram below.

Figure 4. TCLK connection (with Crystal Resonator)

The size of  $C_{L1}$  and  $C_{L2}$  are determined from the crystal manufacturer's specification and the parasitic capacitance of the gm5060 and PCB traces. To avoid start up problems with the internal oscillator, the  $C_{LOAD}$  parameter specified by the crystal manufacturer should not be exceeded.  $C_{LOAD}$  includes  $C_{L1}$ ,  $C_{L2}$  as well as the parasitic capacitances. Specifically, these include the

internal shunt capacitance between XTAL and TCLK ( $C_{SHUNT}$ ), the PCB board capacitance ( $C_{PCB}$ ) and internal pin, pad and ESD protection capacitance. ( $C_{PIN}$ ,  $C_{PAD}$ ,  $C_{ESD}$ )

Figure 5. TCLK parasitic capacitances

$$C_{LOAD} = C_{SHUNT} + ((C_{LOAD1} * C_{LOAD2}) / (C_{LOAD1} + C_{LOAD2}))$$

Where

$$C_{LOAD1} = C_{LJ} + C_{PCB} + C_{PIN} + C_{PAD} + C_{ESD}$$

$$C_{LOAD2} = C_{LOAD1}$$

(i.e.,  $C_{L2} = C_{L1}$ )

The following values can be used for the gm5060:

$C_{SHUNT} \sim 9pF$

$C_{ESD} \sim 5.3 \text{ pF}$

$C_{PAD} \sim 1 pF$

$C_{PIN} \sim 1.1 pF$

C<sub>PCB</sub> is layout dependent (usually 2 to 10 pF)

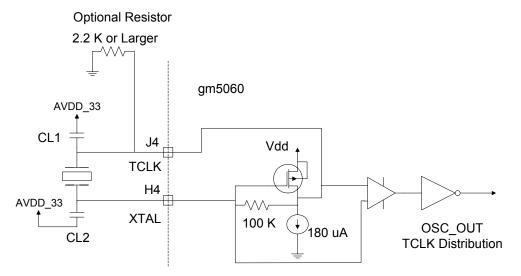

In addition to the above requirement, the crystal should be a parallel resonate cut and the equivalent series resistance must be less than 90 ohms. If the equivalent series resistance is greater than 90 ohms, the oscillator may not start. In this case, the internal oscillator gain may be increased by adding a 2.2 kohm resistor from TCLK pin to ground.

Figure 6. TCLK connection (with Optional Resistor)

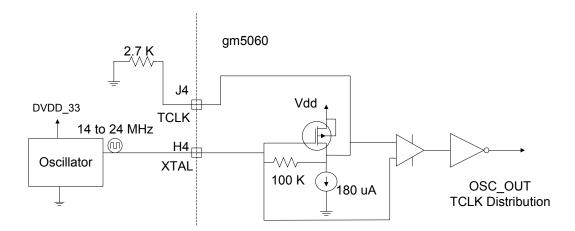

If TCLK is derived from an external oscillator, the applied signal should be made to the XTAL pin. A 2.7 kohm resistor from the TCLK pin to ground provides additional bias to keep the clock symmetrical.

Figure 7. TCLK connection (with Oscillator)

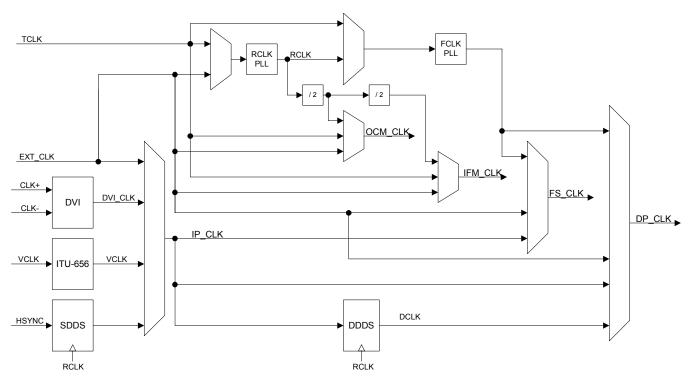

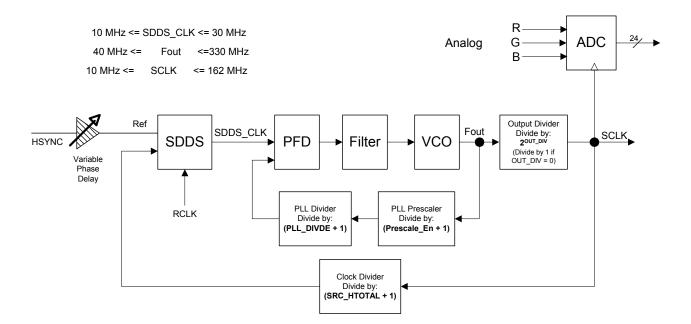

### 4.1.2 Synthesized Clocks

The gm5060 synthesizes all additional clocks internally: Clock inputs to the DDDS and FCLK PLL (as shown in the figure below) are selected via a host interface register.

Note that even when the system is designed without a frame store interface, an internally synthesized frame store clock (FS CLK) is required to clock data in and out of internal FIFOs.

Notes: RCLK nominally ~200 MHz; SDDS=Source Direct Digital Synthesis DDDS = Display Direct Digital Synthesis

Figure 8. Internal Clock Sources

### 4.2 Hardware and Software Resets

#### 4.2.1 Hardware Reset

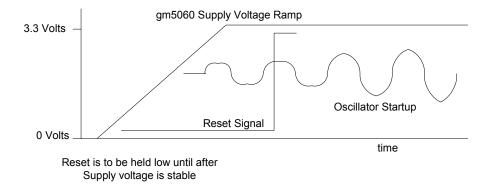

Hardware Reset is performed by holding the RESETn pin low for a minimum of  $1\mu s$  after the supply voltages are stable, as illustrated in Figure 9. A TCLK input (see Clock Options above) must be applied during and after the reset. When the reset period is complete and RESETn is deasserted, the gm5060 follows an internal power up sequence:

- 1. All registers of all types are reset to their default state

- 2. Each clock domain is internally reset. The reset period remains asserted for 64 local clock domain cycles following the de-assertion of RESETn.

- 3. The OCM CLK domain operates at the T CLK frequency during this period.

- 4. The RCLK PLL internally produces a 10x output clock (from TCLK reference).

- 5. The IC will wait for RCLK PLL to Lock and then switch the OCM\_CLK to the bootstrap selected clock.

- 6. The OCM will begin operating if bootstrapped to start operation after Hardware Reset, otherwise it remains in reset until register enabled.

#### 4.2.2 Software Reset

Software Reset is performed by programming the HOST\_CONTROL register bit SOFT\_RESET = '0'. The SOFT\_RESET bit will self clear to '0' upon completion of reset. The following internal operations occur with software reset:

- 1. All active and status registers (i.e. the active part of PA bits, and CRO and RO bits unless otherwise indicated) are reset to their default state. Pending and read/write registers remain unaffected. PA, CRO, and RO bits are defined below:

- Pending and active read write bit. Two registers are used to store these bits: a pending register and an active register. The pending register is transferred to the active register on an update event. The clock domain for each PA register is indicated within square brackets '[]' in the register listing (e.g. the active part of register 0x1B6 DISPLAY\_CONTROL PA [DP\_CLK] will be updated on an update event synchronized to the rising edge of DP\_CLK.)

- Only the active register contents affect chip functionality. The active register bits are cleared to '0', unless otherwise specified, by software or hardware reset. The pending register bits are only cleared by a hardware reset, and may be overwritten at any time.

- **CRO** Clearable read only status bit. These are read only registers that may be cleared to '0' when overwritten with a '1'. This type is most commonly used for interrupt status registers. These are cleared to '0' by both software and hardware reset.

- **RO** Read only status bit. These are read only registers. No effect to the chip will occur if an attempt is made to write to these bits

- 2. Each clock domain in the gm5060 is internally reset for 64 local clock domain cycles, before returning to normal operation.

- Software Reset will NOT reset the analog components of the RCLK PLL, FCLK PLL, SDDS, DDDS, DVI, or ADC blocks. Software reset does not affect the IFM.

Figure 9. Hardware Reset

### 4.3 Analog to Digital Converter

The gm5060 chip has three ADC's (analog-to-digital converters), one for each color (red, green, and blue).

Figure 10. ADC Block

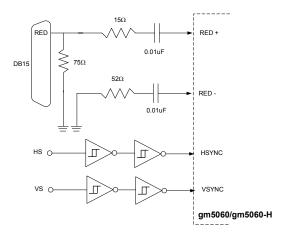

#### 4.3.1 Pin Connection

The RGB signals are connected to the gm5060 as described below:

| Pin Name ADC Signal Name |                                                                           |  |  |  |

|--------------------------|---------------------------------------------------------------------------|--|--|--|

| Red+                     | Red                                                                       |  |  |  |

| Red-                     | Terminate as illustrated in Figure 11                                     |  |  |  |

| Green+                   | Green. When using Sync-On-Green, this signal also carries the sync pulse  |  |  |  |

| Green-                   | Terminate as illustrated in Figure 11                                     |  |  |  |

| Blue+                    | Blue                                                                      |  |  |  |

| Blue-                    | Terminate as illustrated in Figure 11                                     |  |  |  |

| HSYNC/CS                 | Horizontal Sync (Terminate as illustrated in Figure 11) or Composite Sync |  |  |  |

| VSYNC                    | Vertical Sync (Terminate as with HSYNC illustrated in Figure 11)          |  |  |  |

Table 10. Pin Connection for RGB Input with HSYNC/VSYNC

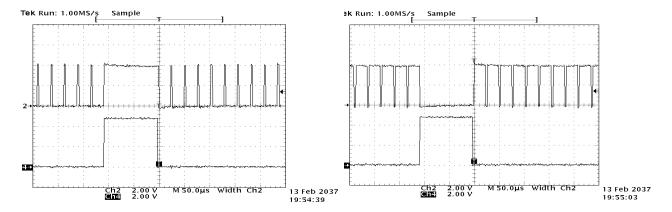

The gm5060 HSync and VSync input pins contain Schmitt trigger with typical hysteresis of 350 mV. It is possible to encounter some combinations of video sources, cable, and PCB layout that will exhibit ringing or glitching at the sync signal edges. In severe cases, the glitching may exceed the internal hysteresis provided and cause "false" triggering within the chip. Using external Schmitt triggers can help eliminate this problem. Figure 11 shows the use of external Schmitt triggers on the Hsync and VSync input pins. A device such as the 74AC14 provides typical hysteresis of 1 volt. Using two Schmitt triggers in series provides a buffered sync signal with very little distortion.

Figure 11. Example Signal Terminations

The negative inputs (eg. RED-) are terminated with an additional 37.5 ohms relative to the positive inputs. This creates a balanced situation for the input amplifier (the positive channel has two 75 ohm terminations in parallel). Please note that it is very important to follow the recommended layout guidelines for the circuit shown above. These are described in "gm5020/5060 System Layout Guidelines" document number C5020-APN-01.

#### 4.3.2 ADC Characteristics

The table below summarizes the characteristics of the ADC:

Table 11. ADC Characteristics

MIN TYP MAX

Track 2 Hold Associations

|                                        | MIN    | IYP         | MAX    | NOTE                                                         |

|----------------------------------------|--------|-------------|--------|--------------------------------------------------------------|

| RGB Track & Hold Amplifiers            |        |             |        |                                                              |

| Bandwidth                              |        | 290MHz      |        |                                                              |

| Settling Time to 1 %                   |        | 5. 2ns      |        | Full Scale Input = 0.75V, BW=290MHz (*)                      |

| Full Scale Adjust Range @ R,G,B Inputs | 0.55 V |             | 0.90 V |                                                              |

| Full Scale Adjust Sensitivity          |        | +/- 1 LSB   |        | Measured @ ADC Output (**)                                   |

| Zero Scale Adjust Range                |        |             |        | AC coupling is used to remove the offset.                    |

| Zero Scale Adjust Sensitivity          |        | +/- 1 LSB   |        | Measured @ ADC Output                                        |

| ADC + RGB Track & Hold Amplifiers      |        |             |        |                                                              |

| Sampling Frequency (fs)                | 20 MHz |             | 162MHz |                                                              |

| Differential Non-Linearity (DNL)       |        | +/-0.5 LSB  |        | fs = 135MHz                                                  |

| Integral Non-Linearity (INL)           |        | +/- 1.5 LSB |        | fs = 135 MHz                                                 |

| Channel to Channel Matching            |        | +/- 0.5 LSB |        |                                                              |

| Effective Number of Bits (ENOB)        |        | 7 Bits      |        | fin = 1 MHz, fs = 80 MHz Vin= -1 dB below full scale = 0.75V |

<sup>(\*)</sup> Guaranteed by design (\*\*) Independent of full scale R,G,B input

The gm5060 ADC has a built in clamp circuit. By inserting series capacitors (10 nF), the DC offset of the video source can be removed. The clamp position and width are programmable.

### 4.3.3 Sync. Signal Support

The gm5060 chip supports digital separate sync (HSYNC/VSYNC), digital composite sync, and analog composite sync (also known as sync-on-green, or SOG). All sync types are supported without the need for external sync separation / extraction circuits.

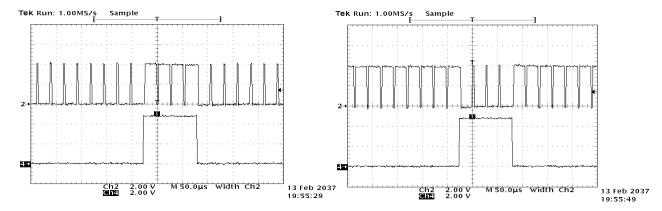

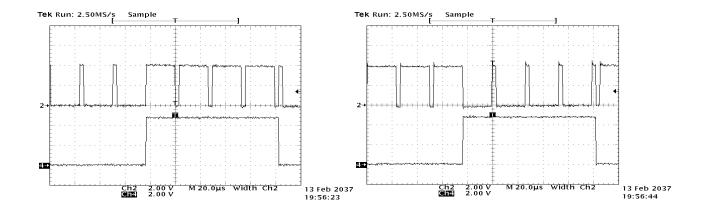

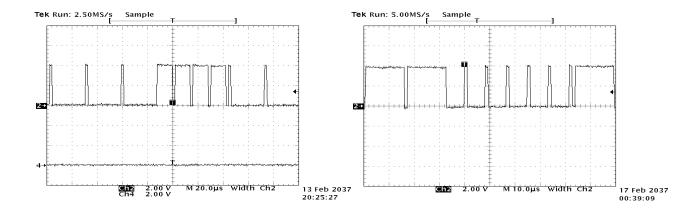

#### **Digital Composite Sync**